摩尔定律的延伸受到物理极限、巨额资金投入等多重压力,迫切需要别开蹊径延续工艺进步。而通过先进封装集成技术,可以更轻松地实现高密度集成、体积微型化和更低的成本。封装行业将在集成电路整体系统整合中扮演更重要的角色,也将对产业的格局形成更多影响。随着先进封装的推进,集成电路产业将展现出一些新的发展趋势,有先进封装的集成电路产业样貎将会有所不同。

先进封装增速远超传统封装

当前社会正处于新技术与新应用全面爆发的背景下,移动设备、大数据、人工智能、5G通信、高性能计算、物联网、智能汽车、智能工业等快速发展。这些技术与应用必将对底层芯片技术产生新的需求。据麦姆斯咨询的介绍,支持这些新兴大趋势的电子硬件需要高计算能力、高速度、更多带宽、低延迟、低功耗、更多功能、更多内存、系统级集成、更精密的传感器,以及最重要的低成本。这些新兴趋势将为各种封装平台创造商机,而先进封装技术是满足各种性能要求和复杂异构集成需求的理想选择。

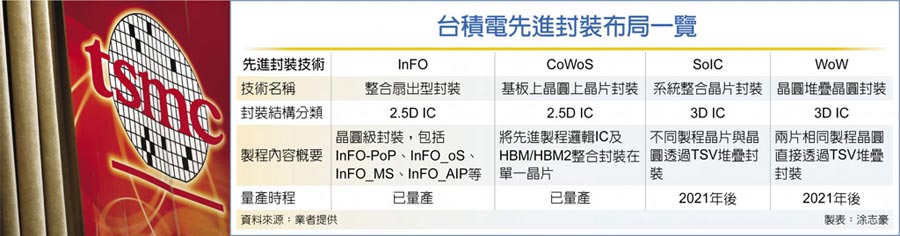

目前来看,扇出型封装(FOWLP/)、系统级封装(SiP)、3D封装是最受关注的三种先进封装技术。扇出型封装是晶圆级封装中的一种,相对于传统封装具有不需要引线框、基板等介质的特点,因此可以实现更轻薄短小的封装。根据IC Insight预计,在未来数年之内,利用扇出型封装技术生产的芯片,每年将以32%的增长率持续扩大,2023年扇出型封装市场规模将超过55亿美元。

系统级封装可以将一个或多个IC芯片及被动元件整合在一个模块中,从而实现具有完整功能的电路集成,它也可以降低成本,缩短上市时间,同时克服了SoC中诸如工艺兼容、信号混合、噪声干扰、电磁干扰等难题。

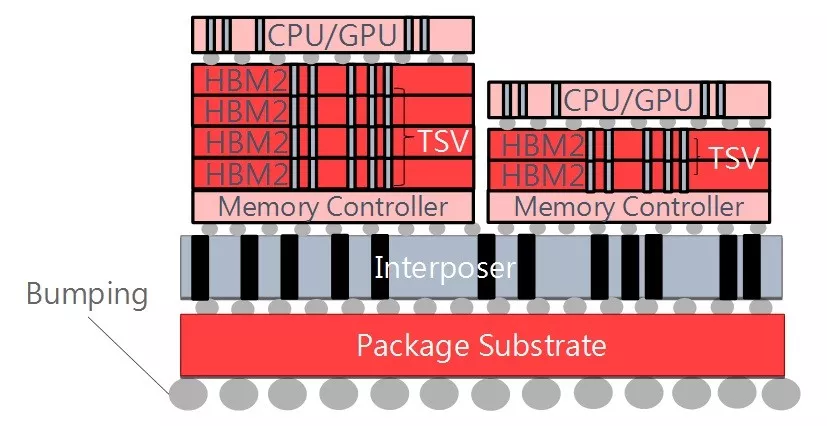

3D封装通过晶圆级互连技术实现芯片间的高密度封装,可以有效满足高功能芯片超轻、超薄、高性能、低功耗及低成本的需求,被大多半导体厂商认为是最具有潜力的封装方法。

总之,在市场需求的带动下,越来越多先进封装技术被开发出来,先进封装的市场占比将会进一步扩大。统计数据显示,从2017年到2023年,整个半导体封装市场的营收将以5.2%的年复合增长率增长,而先进封装市场将以7%的年复合增长率增长,市场规模到2023年将增长至390亿美元,传统封装市场的复合年增长率则低于3.3%。

展现三大发展趋势

随着先进封装技术的发展以及市场规模的扩大,其对于整个集成电路产业结构将产生越来越大的影响。首先是中段工艺的出现并逐渐形成规模。随着传统封装技术向先进封装过渡,有别于传统封装技术的凸块(Bumping)、再布线(RDL)、硅通孔(TSV)等中段工艺被开发出来,并且开始发挥重要作用。中芯长电半导体首席执行官崔东表示,仅靠缩小线宽的办法已经无法同时满足性能、功耗、面积,以及信号传输速度等多方面的要求,因此半导体企业开始把注意力放在系统集成层面来寻找解决方案,也就是通过先进的硅片级封装技术,把不同工艺技术代的裸芯封装在一个硅片级的系统里,兼顾性能、功耗和传输速度的要求。这就产生了在硅片级进行芯片之间互联的需要,进而产生了凸块、再布线、硅通孔等中段工艺。而中段硅片加工的出现,也打破了前后段芯片加工的传统分工方式。

其次,制造与封装将形成新的竞合关系。由于先进封装带来的中段工艺,封测业和晶圆制造业有了更紧密的联系,在带来发展机遇的同时,也面临着新的挑战。中段封装的崛起必然挤压晶圆制造或者封装测试业的份额。有迹象表明,部分晶圆厂已加大在中段封装工艺上的布局。晶圆厂有着技术和资本的领先优势,将对封测厂形成较大的竞争压力。传统封测厂较晶圆制造业相比属于轻资产,引入中段工艺后,设备资产比重较传统封装大大增加,封测业的先进技术研发和扩产将面临较大的资金压力。

最后,推动集成电路整体实力的提升。后摩尔时代的集成电路产业更强调产业链的紧密合作,强化产业链上下游之间的内在联系,要求各个环节不再是割裂地单独进行生产加工,而是要求从系统设计、产品设计、前段工艺技术和封测各个环节开展更加紧密的合作。企业对于先进封装业务的竞争,最终还需表现为产业链之间综合实力的竞争。

中国应加快虚拟IDM生态链建设

近几年中国集成电路封测产业实现了高速发展,有了长足的进步,然而国内集成电路封测产业链整体技术水平不高也是不争的事实。半导体专家莫大康认为,中国现在非常重视集成电路产业,推动先进封装业的发展就是非常必要的了。中国的封装测试是集成电路三业(设计、制造、封测)中起步最早的,与国际水平差距也比较小,因此完全有能力发展起来。

华进半导体总经理曹立强在近日的演讲中再次提出,推动国内“EDA软件—芯片设计—芯片制造—芯片封测—整机应用”集成电路产业链虚拟IDM生态链的建设,以市场需求牵引我国集成电路封测产业快速发展。集成电路的竞争最终会表现为产业链之间综合实力的竞争,先进封装的发展需要从工艺、设备和材料等方面的协同。

在新的技术趋势和竞争环境下,集成电路产业越来越表现为产业链整体实力的竞争。过去几年,国际半导体制造公司纷纷加大力度向先进工艺挺进,在持续大规模资本投入扩建产能的带动下,一些半导体制造大厂同样具备了完整的先进封装制造能力。

应对这样的产业形势,曹立强指出,重点在于突破一些关键性技术,如高密度封装关键工艺、三维封装关键技术、多功能芯片叠层集成关键技术、系统级封装关键技术等。建设立足应用、重在转化、多功能、高起点的虚拟IDM产业链,解决集成电路产业领域的关键技术,突破技术瓶颈。