近几年AI芯片火热,不让Nvidia专美于前,英特尔在确定进入10纳米时代后更是积极追赶,美国时间20日,英特尔公布首款神经网络处理器Nervana(代号Springhill)相关细节,包含训练芯片NNP-T与推论芯片NNP-I,加上原有的Xeon在AI芯片阵容越发坚强,技术也开始兼容了起来。

美国时间20日,英特尔在今年Hot Chips大会上公布首款神经网络处理器Nervana细节,如其名,这是2016年英特尔收购包含Nervana几家新创公司的成果。Nervana处理器分为训练芯片NNP-T与推论芯片NNP-I。

训练用的Nervana NNP-T,主打可编程与灵活性,并强调可从头建构大规模深度学习模型,且尽可能训练电脑在给定的能耗预算内快速完成任务,也无需传统技术的庞大开销。

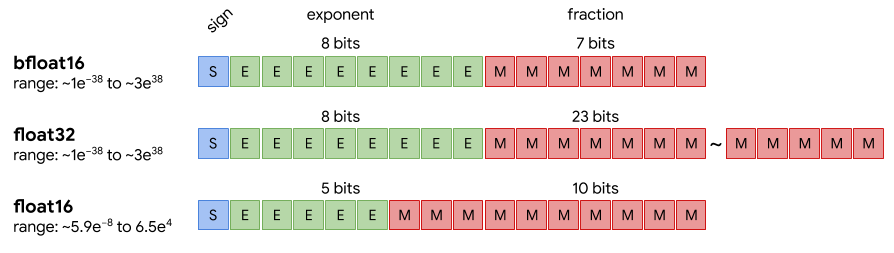

NNP-T支援了Google TPU Tensorflow架构特有的运算格式“bfloat16”,bfloat16截断既有的32位元float32的前16位,仅留下后16位所组成,在许多机器学习模型可以容忍较低精确度计算、不需降低收敛准确率的情况下,许多模型使用bfloat16达到的收敛准确率结果与一般使用的32位元浮点(FP32)计算数值的结果一样,降低精度其实能让存储器效率取得较佳的平衡,从而训练与部署更多的网络、降低训练所需的时间,有较好的效率与灵活性,而这是英特尔首次将bfloat16内建于处理器。

▲bfloat16浮点格式(Source:Google)

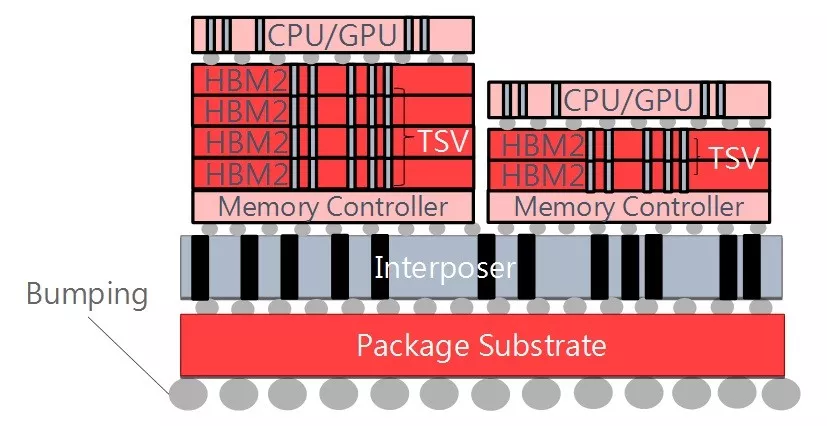

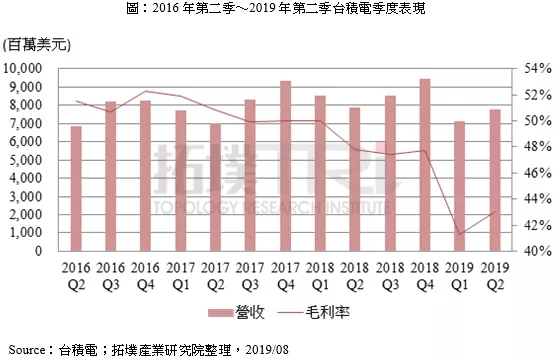

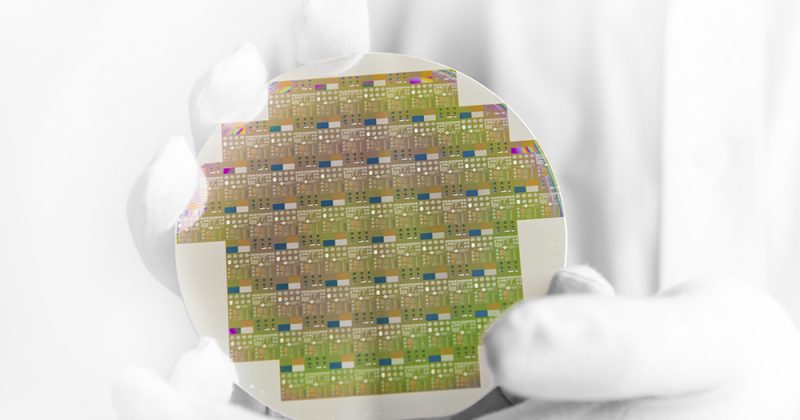

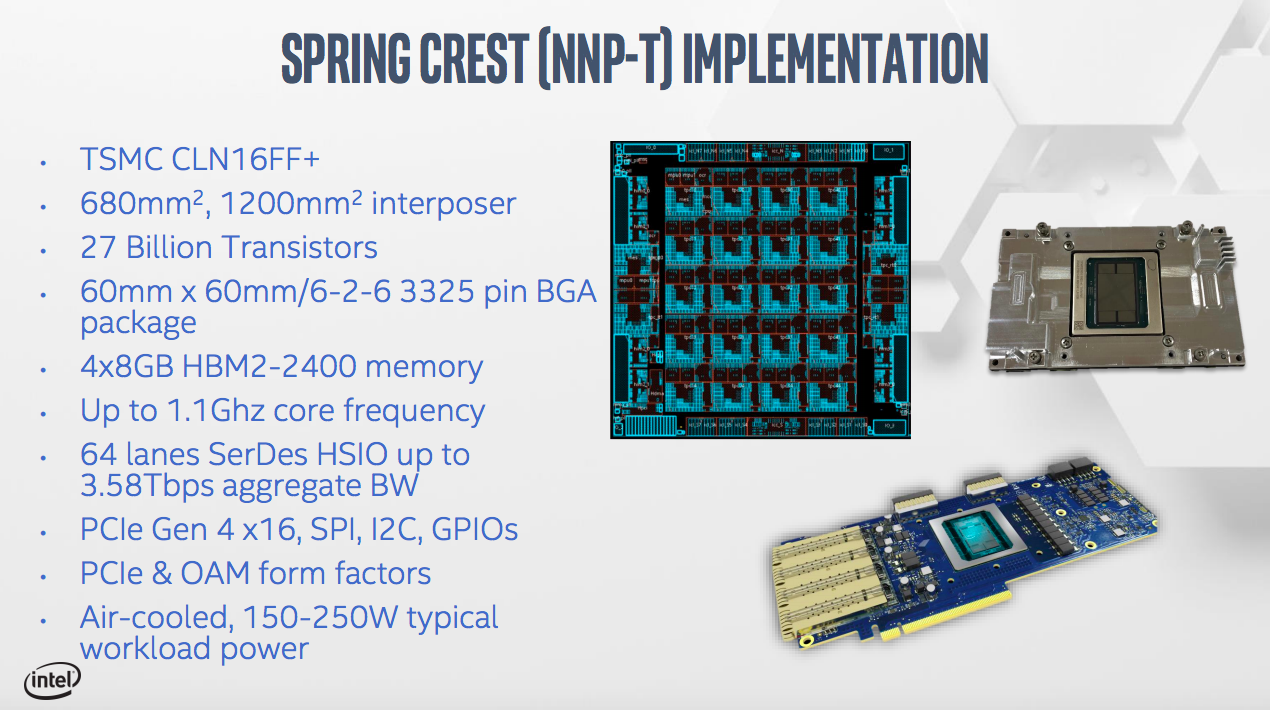

另外有趣的是NNP-T其实采用的是台积电16纳米CLN FF+制程,这与一般我们对英特尔自行生产芯片的认知有所差异,而在Nervana被英特尔收购前,第一代Lake Crest就是由台积电所代工。NNP-T采用台积电最新的CoWoS(Chip on Wafer on Substrate)封装技术,将NNP-T的晶粒与四个8GB HBM2存储器异质整合堆叠2.5D,让其封装体积缩小成一个60X60 mm的芯片。

▲Nervana NNP-T采用台积电16nm CLN FF+制程(Source:Intel)

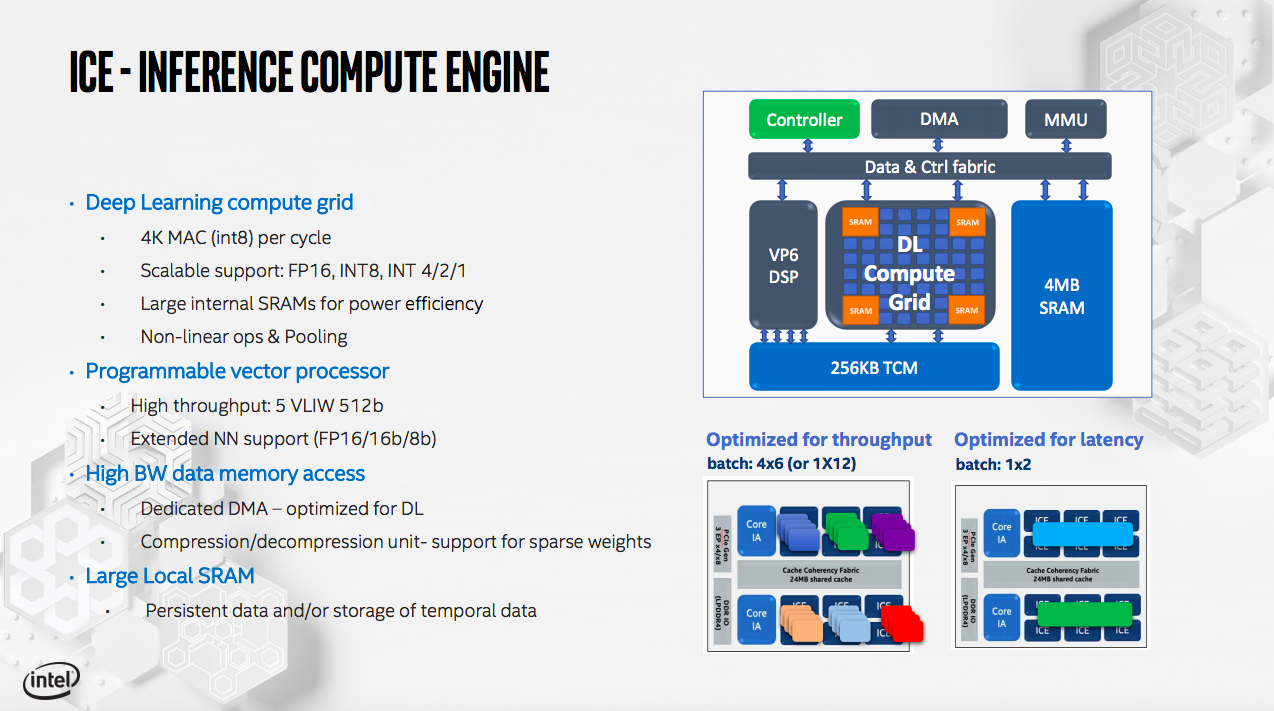

英特尔同时发表了推论芯片Nervana NNP-I,主要针对大型资料中心市场高效能深度学习推论而生,NNP-I主要基于英特尔10nm Ice Lake处理器,官方强调透过此芯片,可提高每瓦效能,让企业以更低的成本执行推论运算工作,降低推论大量部署的成本。英特尔指出,NNP-I在功率10瓦下每秒能处理3600张影像,而处理器本身亦拥有高度可编程性,且同时不影响性能与功效。

▲Nervana NNP-I架构(Source:Intel)

NNP-I已与Facebook合作并实际运用在其相关业务上,而NNP-T将于今年底以前针对尤其云端服务商相关的高端客户送样,并在2020年之前拓展市场。