近期电子科技大学张波教授提出“特色工艺将成为中国半导体业的机遇”,由于有独特的见解,已引发业界的赞许。

特色工艺这个词有些“新”,但是经张波教授的解释,它原是摩尔定律的三个方向之一,英语叫“More Than Moore”,之前的译名为“超越摩尓定律”。

张波教授把“特色工艺”称为“非尺寸依赖”, 是指器件价值或者性能的提升,不完全靠尺寸缩小,而是通过功能的增加。

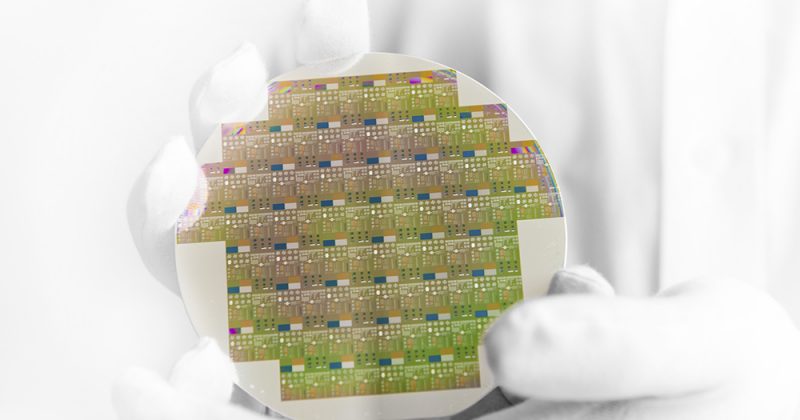

实际上定律延续50多年来,半导体业的驱动力有两个,一个是尺寸缩小,另一个是硅片直径增大,显然尺寸缩小起主要作用。

由于定律有自身的局限性,在那个时代它只能预测到晶体管的密度要增加,成本可下降,实际上它无法揭示随之而来的功耗增大及晶体管的性能提高等。所以近期指出定律的另一个方向,”非尺寸依赖”具有指导意义。

为什么特色工艺成香饽饽

全球半导体业在2000年时销售额达2000亿美元,至2013年,经过13年时间达到3000亿美元,然而仅用了4年时间,至2017年时己上升到4000亿美元,而2018年达到4700亿美元,非常可能在2020年时达到5000亿美元。它反映全球电子产品市场中硅含量的急速提升及价值链的体现。

但是从另一方面观察,由于定律不可避免的趋向物理极限,IC设计成本的急速飙升,全球能够继续追踪尺寸缩小的厂商数量越来越少,导致依赖工艺尺寸缩小的推动力减弱。所以半导体业界试图开辟另一个战场,所谓特色工艺其理在其中。

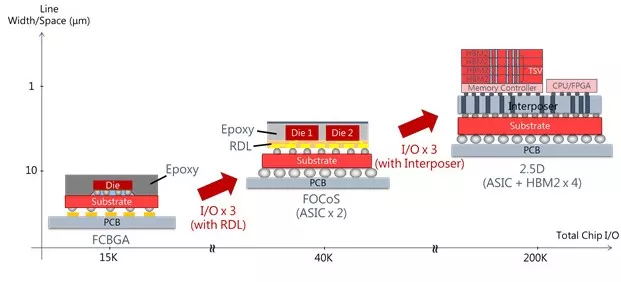

依业界的观点,特色工艺主要指模拟、RF、功率及MEMS,以及近期非常火热的2.5D、3D的堆叠封装等。在未来20年中它非常可能成为主要推动力之一。

按现在的认识,特色工艺可能集中于8英寸硅片,及少部分的12英寸硅片中,从工艺尺寸覆盖可能在28nm以上。显然这个分界线逐步在改变,在2000年时12英寸硅片刚兴起时,这个分界线是90nm。如今8英寸硅片逐步升级也己扩展到65nm。这一切取决于经济因素,因为升级8英寸设备要投资,以及90nm以下的光刻机需要重新购买,增加了成本。

如果采用8英寸硅片设备作特色工艺,有它的独特优势:1),设备的折旧期已过,节省成本;2),250nm-130nm工艺相对成熟稳定;3),设备的软件升级较少受原厂控制等。

张波教授总结特色工艺具有市场分散,品种众多、与应用关系强,且无垄断企业等特点。

但是仔细罗列全球摸拟,RF,功率及MEMS等全球前十位厂商中,发现排在前列的都是历史悠久的资深老厂,如欧洲的NXP、Infineon及STMicron及日本的Sony、东芝、三菱、富士通、瑞萨、及美国的TI、Microsemi、及ON Semi等。其中许多厂商至今仍坚守8英寸,甚至6英寸硅片,但是有举足轻重的地位。

据SEMI 2015年数据,2016年全球8英寸硅片的市场份额,模拟占11%,分立器件14%,逻辑加微处理器21%,存储器占3%,代工占47%及MEMS加其它占4%。

另据SEMI 2016年数据,2017年全球晶圆产能为每月1790万片(8inch计),其中8英寸产能为月产520万片,约占不到1/3,其中前十大8英寸厂的产能占总产能的54%。

特色工艺在中国

据厦门半导体投资集团总经理王汇联的数据,2018年中国在建及规划Fab产线总共33条,包括21条12英寸线、11条8英寸线,其中特色工艺线16条、逻辑产线9条、存储产线8条。SEMI数据显示中国晶圆产能2019年占到全球16%,到2020年将增至20%。

其中的趋势是中芯国际,代工业的领头羊,除了在国家资金等支持下,开发14nm及以下逻辑制程工艺之外,积极扩充它的8英寸产能,包括天津,深圳,宁波,绍兴等地,而原本生存得很滋润的华虹,华润微电子,士兰等,却由8英寸延伸至12英寸,目的都是为了实现产品差异化,跨入特色工艺中。

实际上企业的决策才是最真实的反映,它们的感觉十分灵敏及深刻。那么多条特色工艺生产线的兴建,至少反映现阶段它可能适合于中国半导体业发展的需要。

因为从产业利益出发,现阶段由中芯国际,华力微积极跟踪14nm及以下逻辑制程,以及由长江存储做3D NAND闪存,合肥长鑫做19nmDRAM等都是很有必要,首先要解决“0”到“1”的突破问题,具备能力之后才逐步扩充产能。显然这段路十分崎岖,投资巨大及周期长,技术难度高,未来产品市场的竞争力将经受考验。

而绝大部分的中国半导体企业,它们首要任务是求生存,能实现盈利,所以让它们去追踪定律,或者尝试存储器的IDM模式量产是不客观的。所以它们纷纷转向选择特色工艺可能是必由之路。

分析中国半导体业在代工业中8英寸制程与全球的先进水平接近,有一定优势,但是在非逻辑制程中,如模拟、高压、MEMS、包括IDM模式的产品等方面可能差距较大。

另据张波教授的资料,采用特色工艺可能有助于提高国产化率。因为中国进口集成电路的均价只有7毛五,不足一美元。其中进口了大量每块价值达数百美元的高端CPU,同时也大量进口了不需要先进工艺的分立器件、电源管理IC、微控制器等。因此釆用特色工艺,国产替代的空间非常巨大。

显然在市场竞争中,对于中国半导体业发展不可能有一条“捷径”,做特色工艺是机遇与风险同在。因为对手都十分强大,经验丰富,而我们是“追赶者”,从先天性方面不存在优势,仅仅是由于市场机会多,产品分散,与应用结合强,而中国拥有全球最大的市场,具这样的优势地位有可能让我们从中分得一杯羹。

企业成功的要素取决于市场空间,技术能力及时机,关键要有一位强有力的CEO。

近期贸易战对于中国半导体业发展的影响不可小视,一个是电子产业链有部分外移出中国,另一个是美国的封锁持续加紧等,导致中国半导体业要维持年均增长率达20%可能有一定难度。不过事物有它的“两重性”,有时“坏事”也可能变成“好事”,如贸易战下促使部分人才加速回流,以及在外压力下能激发斗志,更加团结,有可能取得更大的成绩。