前不久英特尔联合加州大学伯克利分校的研究人员开发了一种新的MESO(磁电自旋轨道)逻辑器件,其工作电压可以从3V降低到500mV,能耗减少10-30倍,性能提升5倍,该技术有望取代现有的CMOS半导体工艺,成为未来计算技术的基础。英特尔对这个技术很重视,在宣传上也不遗余力,这种情况在以往可不多见,毕竟普通人对枯燥的技术是没兴趣了解的。

提到半导体工艺,在这个问题上英特尔被骂了很多年的“挤牙膏”,但事实上英特尔这几年来在CPU架构、指令集及工艺上还是有不少进展的,不过从2014年14nm节点到现在,英特尔在CPU处理器上确实没有取得明显进展,以往两年一升级的Tick-Tock钟摆战略也完了,所以英特尔被玩家调侃挤牙膏不是没理由的。

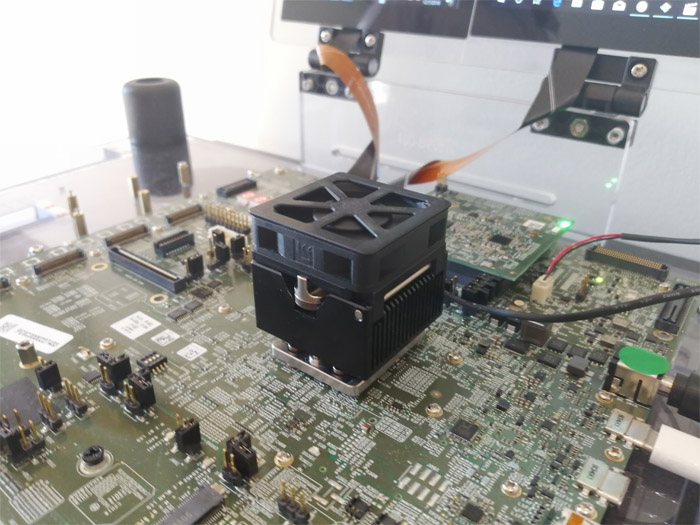

在上周的英特尔架构日活动上,英特尔一反常态地公布了多项CPU架构、半导体工艺、芯片封装以及核显、独显架构上的进展。这次会议虽然规模很小,但是影响深远,标志着英特尔在未来的芯片架构、工艺上的重大变化。今天的超能课堂我们就来聊聊英特尔的这些变化,特别是Sunny Cove架构及3D封装Foreros技术。

“摩尔定律”到头了,线宽微缩终有尽时

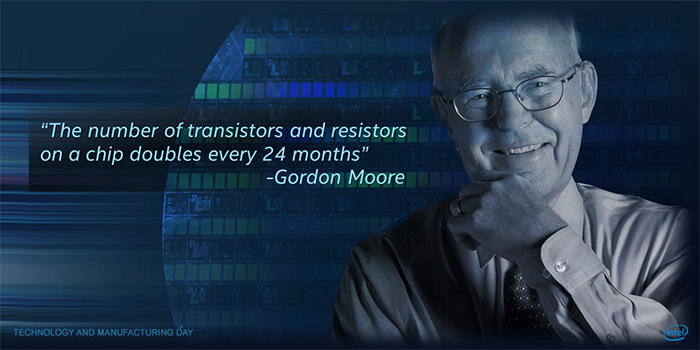

如果说英特尔近年来遭遇的难题以及这次转变,绕不过的一个话题就是摩尔定律,它的提出者戈登·摩尔是英特尔创始人之一,当年提出摩尔定律时还没有创立英特尔,1965年《电子学杂志》发表了时任仙童半导体工程师戈登·摩尔的一篇文章,他在文中预言半导体芯片上的晶体管数量会以每年翻倍的速度增长,这个就是“摩尔定律”的由来,这个定律随后也在不断修正,1975年摩尔将其改为每2年晶体管数量翻倍。

摩尔定律

摩尔定律在过去50年中成为半导体行业的金科玉律,指导着行业技术发展,英特尔也成为摩尔定律最坚定的支持者,之前的Tick-Tock战略实际上就是摩尔定律的变种,2年升级一次工艺、架构,每次升级都会大幅降低晶体管成本,提升晶体管密度。

但是摩尔定律没法一直持续下去,随着晶体管的不断缩小,人们开始遇到两个问题,一个是技术上的,10nm节点及之后,CMOS工艺的栅极氧化层越来越薄,可能只有10个原子的厚度,导致量子效应愈加严重,而光刻工艺也会越来越难,目前的预测是5nm节点实际上就是摩尔定律的终结了。

除了技术原因,经济效应越来越低也是摩尔定律终结的重要原因,此前半导体工艺升级会带来成本下降,但是随着工艺微缩困难增加,半导体制造使用的先进材料、多重曝光以及EUV光刻机等都会大幅增加制造成本,晶体管微缩带来的成本降低已经被增加的成本抵消了。

对于摩尔定律,FinFET工艺及FD-SOI工艺的发明人、加州大学伯克利分校教授,IEEE院士、美国工程院院士、中科院外籍院士胡正明之前提到过“集成电路的发展路径并不一定非要把线宽越做越小,现在存储器已经朝三维方向发展了。当然我们希望把它做得更小,可是我们也可以采取其他方法推进集成电路技术的发展,比如减少芯片的能耗。这个方向芯片还有1000倍的能耗可以降低。线宽的微缩总是有一个极限的,到了某种程度,就没有经济效应,驱动人们把这条路径继续走下去。但是我们并不一定非要一条路走到黑,我们也可以转换一个思路,同样可能实现我们想要达到的目的。”

英特尔解绑芯片架构与工艺,向3D封装进发

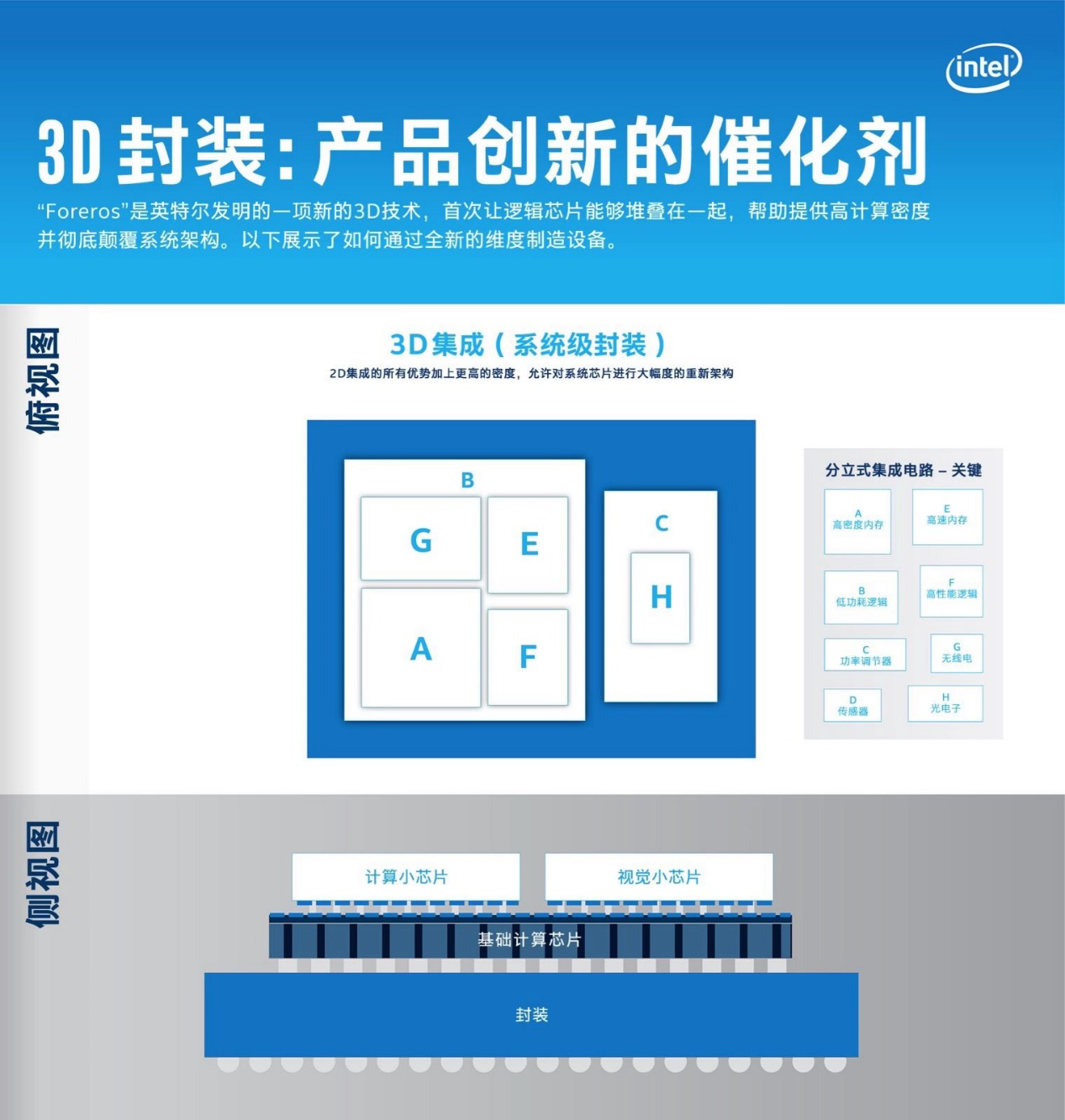

尽管英特尔嘴上依然不承认摩尔定律终结,但是这次的架构日上英特尔并没有提及10nm工艺以及未来的7nm工艺具体进展,他们重点介绍的其实不是制造工艺,而是新型封装技术Foveros,而3D封装也被视为后摩尔定律时代的一个方向,这也是上面胡正明教授所说的不要一条道走到黑,转换思路的结果。

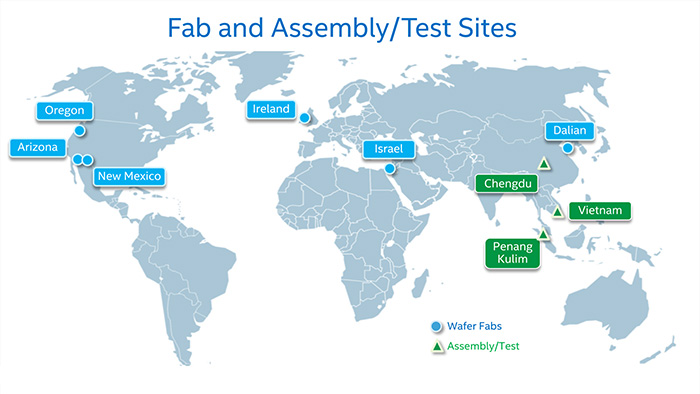

英特尔是一家IDM垂直整合型半导体公司,自己设计芯片架构,自己生产芯片,然后自己封装芯片。就CPU业务来说,以往的时候,英特尔会针对不同的工艺开发不同的CPU架构,针对新工艺开发的架构可以最大化利用工艺优势,但是缺点就是架构与工艺捆绑起来,不够灵活,这也是为什么英特尔10nm工艺不断延期,英特尔不能使用14nm生产10nm架构,只能耗着等的原因。

现在英特尔学乖了,工艺跟架构分离,万一工艺延期了,CPU架构也不用干等着,理论上英特尔现在就可以用14nm工艺生产原本用于10nm工艺的Ice Lake处理器了。不仅如此,英特尔现在还更上一层楼,带来了全新的Foveros 3D封装。

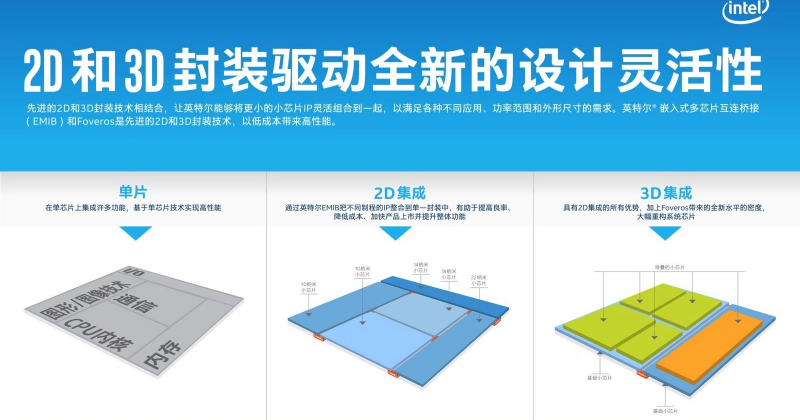

为了让大家理解Foveros封装,英特尔做了很详细的解释,简单来说就是单片时代处理器内部的CPU核心、GPU核心、IO单元、内存控制器等子单元都是同一工艺的,但是不同的单元实际上对工艺的需求不同,CPU、GPU核心对性能要求高,上先进工艺是值得的,但是IO单元、控制器单元不需要这么先进的工艺,所以他们是可以使用不同工艺然后集成到一起的。

在Foveros之前,英特尔推出了EMIB封装技术,就是把不同的工艺的IP核心集成到一起,而Foveros封装更进一步,不仅具备2D封装的所有优势,还能大幅重构系统芯片。

根据英特尔所说,该技术提供了极大的灵活性,因为设计人员可在新的产品形态中“混搭”不同的技术专利模块与各种存储芯片和I/O配置。并使得产品能够分解成更小的“芯片组合”,其中I/O、SRAM和电源传输电路可以集成在基础晶片中,而高性能逻辑“芯片组合”则堆叠在顶部。

英特尔预计将从2019年下半年开始推出一系列采用Foveros技术的产品。首款Foveros产品将整合高性能10nm计算堆叠“芯片组合”和低功耗22FFL基础晶片。它将在小巧的产品形态中实现世界一流的性能与功耗效率。

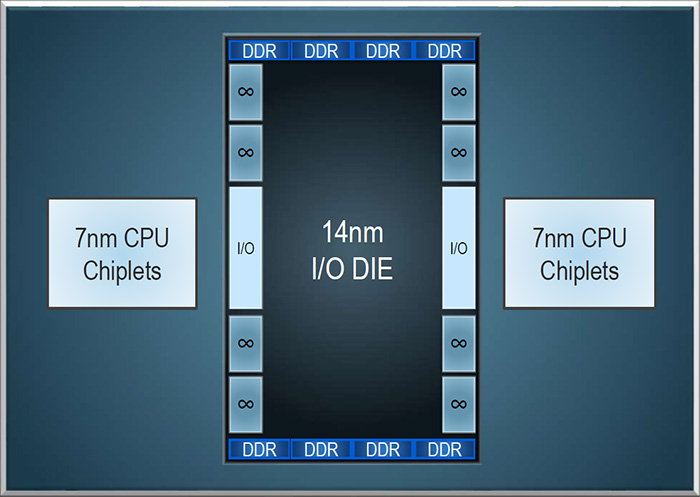

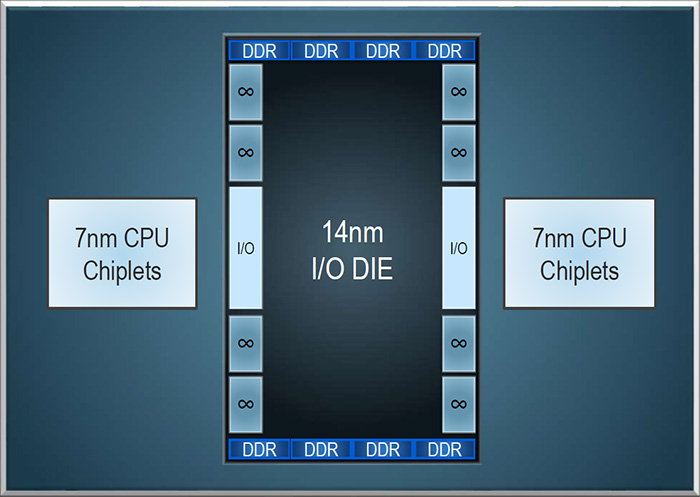

AMD在Zen 2处理器上也使用了类似的封装

在使用3D封装提升芯片性能、集成度方面,英特尔其实不孤独,在他们之前AMD在7nm Zen 2处理器上也使用了类似的理念,其CPU核心使用先进的7nm工艺制造,IO核心、内存控制器等单元使用的是14nm工艺,然后将两个子单元封装在一起。

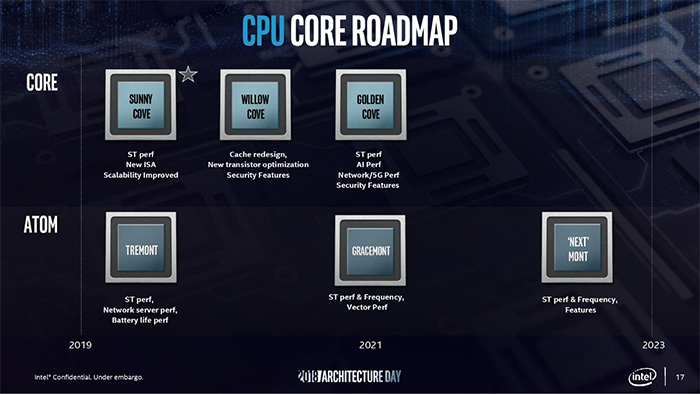

英特尔Core内核路线图:大小核时代来临,Sunny Cove首发

在通过Foveros 3D封装技术“解决”工艺问题之后,英特尔还需要在CPU架构升级来提升IPC性能,因为现在14nm+++工艺潜力挖掘差不多了,哪怕是未来的10nm工艺量产了,性能恐怕也是无法大幅超越14nm工艺的,所以CPU架构对英特尔的作用比以往更重要。

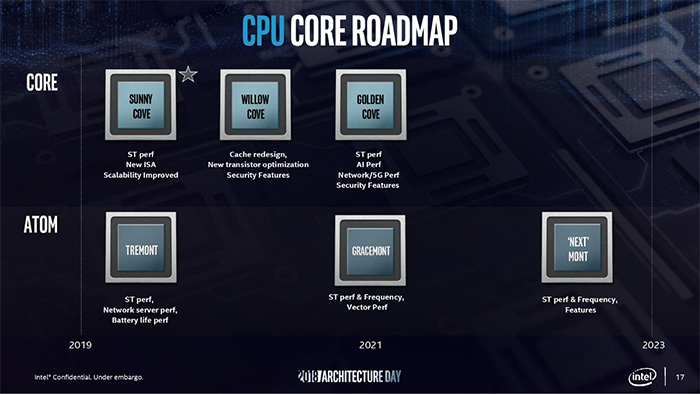

在架构日上,英特尔也更新了Core内核路线图,实际上是分为两个类别的,大核心是Core系列,首发的是Sunny Cove微内核,主要聚焦在ST单核性能、全新ISA及并行性三个方面,之后是Willow Cove,改进重点是缓存、晶体管优化、安全功能,再往后是Goden Cove内核,重点是ST单线程、AI性能、网络/5G、安全功能等。

Atom处理器的小核心路线图升级周期比Core更长,明年首发的是Trement,重点提升ST单线程性能、网络服务器及续航,2021年还会有Gracemont,重点提升单线程性能及频率、矢量性能,再往后的架构还没确定,只是一个方向了。

对PC玩家来说,最期待的还是Sunny Cove架构,2019年开始它会是英特尔下一代服务器及PC处理器的主力架构。根据英特尔所说,该架构主要改进是:

·增强的微架构,可并行执行更多操作。

·可降低延迟的新算法。

·增加关键缓冲区和缓存的大小,可优化以数据为中心的工作负载。

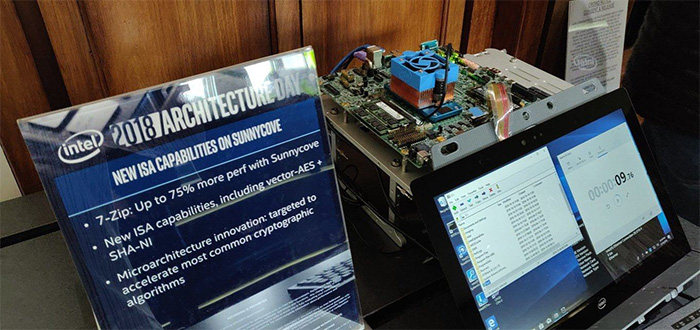

·针对特定用例和算法的架构扩展。例如,提升加密性能的新指令,如矢量AES和SHA-NI,以及压缩/解压缩等其它关键用例。

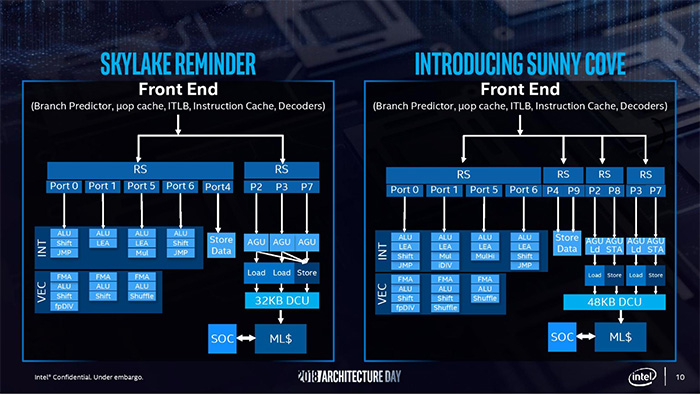

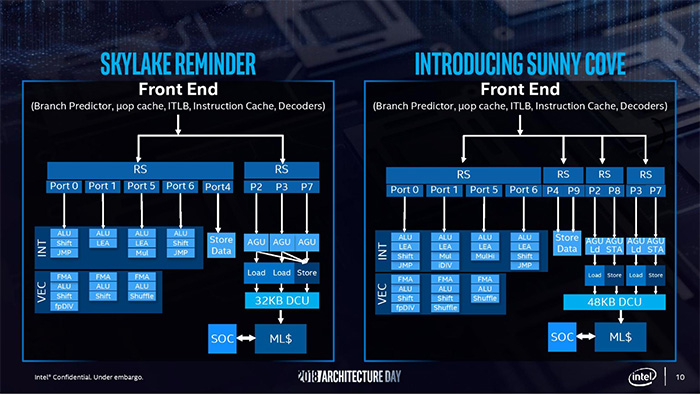

Sunny Cove架构与Skylake架构对比

上图就是Sunn Cove(右)与现有的Skylake架构(左)的渲染流水线对比,后者是2015年发布的架构了,第一代14nm处理器Broadwell由于进度关系没产生什么影响力,而Skylake架构一直衍生出了Kaby Lake、Coffee Lake、Wisky Lake、Cascade Lake等架构,在移动、桌面及服务器领域全面开花。

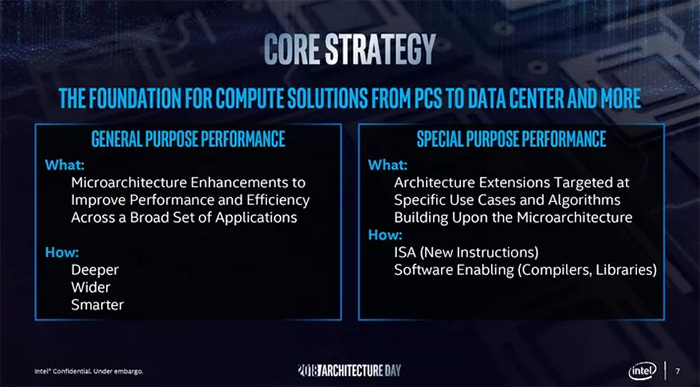

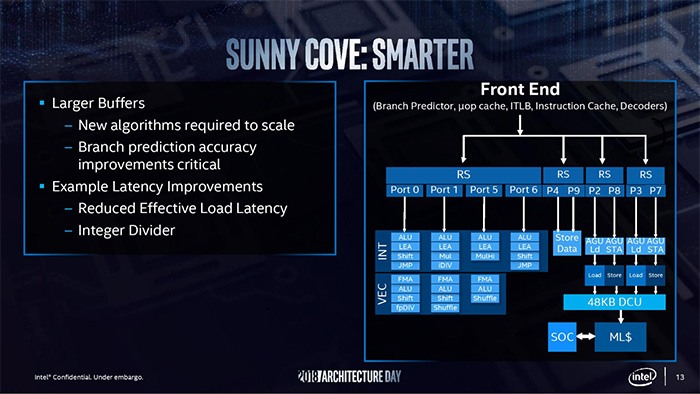

在如何实现CPU IPC性能提升的方式上,英特尔总结了三个字——更深(deeper)、更宽(wider)、更智能(smarter),全面提升从前端到执行单元的性能、位宽。

在更深方面,Sunny Cove的L1数据缓存从32KB增加到48KB,增加了50%,L2缓存、uop缓存、二级TLB缓存都加大了。

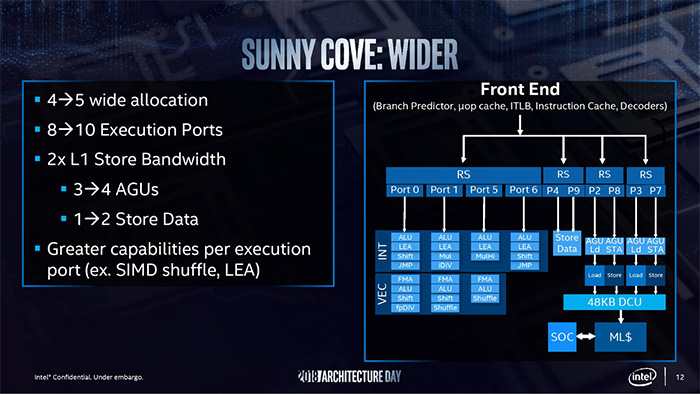

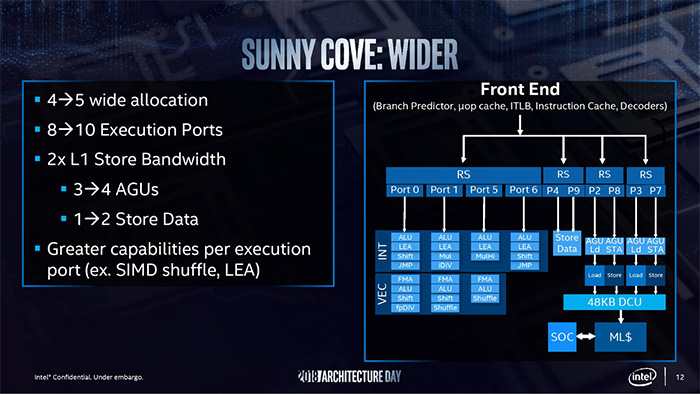

在执行管线上,Sunny Cove的分配单元从目前的4个增加到5个,执行接口从8个增加到10个,L1 Store带宽翻倍。

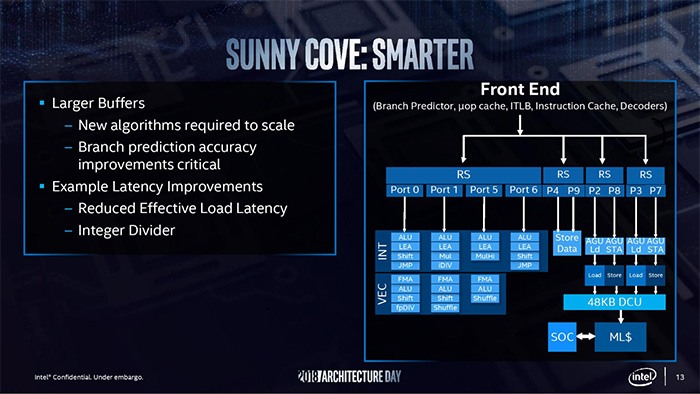

前面增加缓存、提升操作次数的设计还需要搭配更好的算法,所以Sunny Cove还要更加智能,提高分支预测的精度,减少延迟等等。

专业性能提升

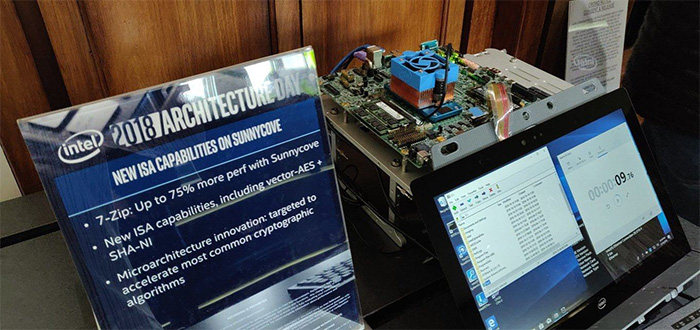

除了前面的更宽、更深、更智能之外,Sunny Cove架构在专业性能上也有改进,大家可能还记得最早爆料架构日新内容的时候就有7-Zip性能提升75%的爆料,这就是Sunny Cove架构了加密解密指令集的缘故,其他还有AI、内存、网络、矢量等方面的改进。

全新加密指令可以大幅提升7-Zip的性能

英特尔版的big.LITTLE大小核策略:Sunny Cove与Tremont合体

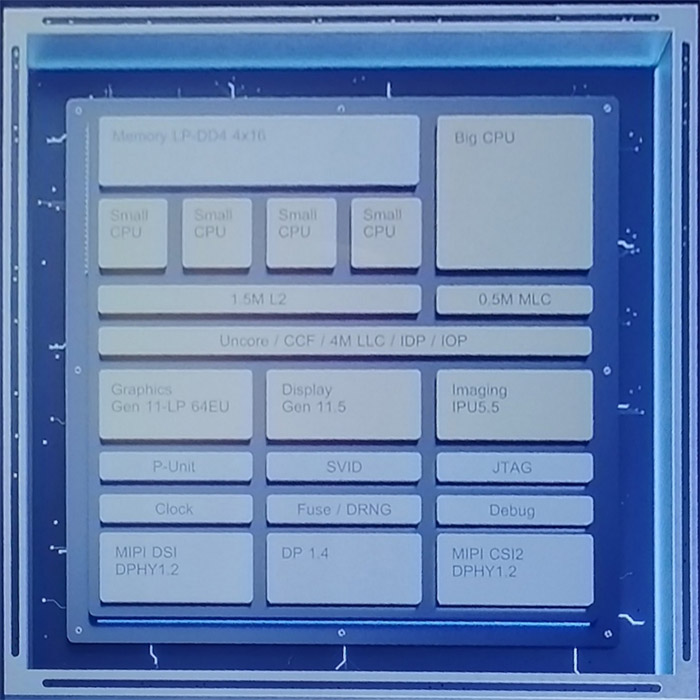

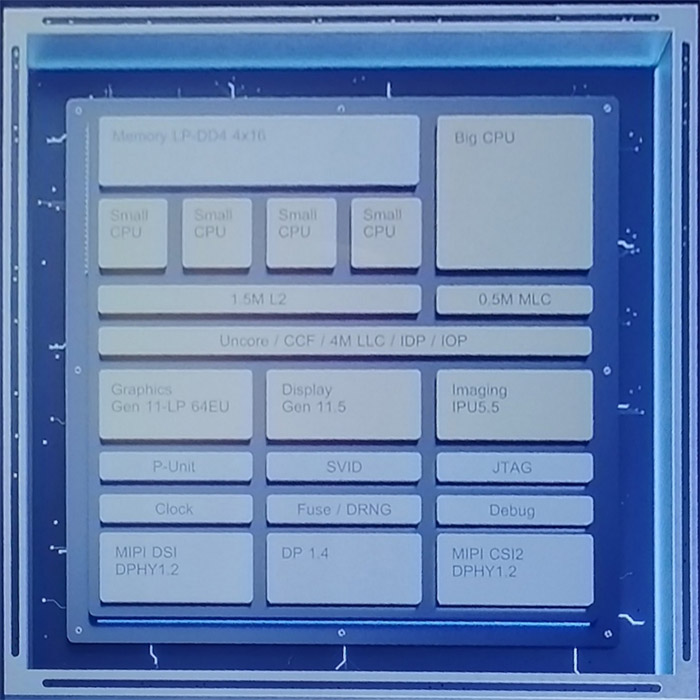

在拥有了Sunny Cove大核以及Tremont小核之后,再加上3D封装技术Foveros,英特尔终于可以做一些不同寻常的产品了。在架构日当天,英特尔就展示了一种混合X86处理器,大核是Sunny Cove,小核是Tremont,整合了22nm工艺的IO核心以,共享1.5M L2缓存,所有核心共享4MB的LLC缓存,内存控制器是4*16位的,支持LPDDR4,整合了Gen 11核显,有64个EU单元,Gen 11.5显示控制器还有新的IPU,支持DP 1.4。

英特尔的这个混合X86处理器就是很早之前曝光的“Lakefield”的处理器,它将采用“Ice Lake”高性能内核和“Tremont”低功耗内核,它主要是给移动市场准备的,类似ARM公司的big.LITTLE大小核架构,需要高性能运算的时候使用大核心,否则使用低功耗核心以降低功耗。

在这个混合X86处理器上,占用空间小也是个优势,其尺寸只有12*12*1mm,相当于一个10美分硬币大小,而且待机功耗只有2mW,低功耗+小体积的优势非常适合各种移动设备,有助于英特尔更好地跟ARM等移动处理器竞争,守卫自己的领地。

总结:英特尔灵活应对后摩尔定律时代,再战AMD 7nm

总之, 一直自诩为摩尔定律守卫者的英特尔也不得不考虑后摩尔时代的生存问题了,架构日上他们还是避而不谈10nm工艺以及未来的7nm工艺,如果还是像过去那样等着先进工艺量产才来升级CPU架构,那么在面对早早采用模块化设计思路的AMD竞争时,英特尔只怕更无力应对。

Foveros 3D封装及Sunny Cove就是英特尔给出的答案,通过封装不同工艺水平的芯片解决了工艺升级的问题,而全新设计的Sunny Cove架构(还有Gen 11核显这里没重点介绍)也进一步提高了Ice Lake处理器的IPC性能。

根据英特尔的消息,2019年他们就会推出Foveros 3D封装技术的新一代10nm+22nm工艺Sunny Cove处理器,整合Gen 11核显,而AMD明年推出的是7nm+14nm工艺的Zen 2处理器及Navi GPU核心。虽然目前还不知道这两家公司具体的桌面处理器规格,但是2019年有好戏看是没跑了。