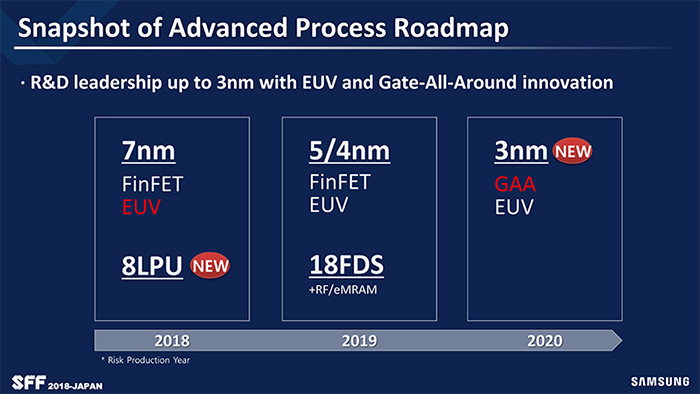

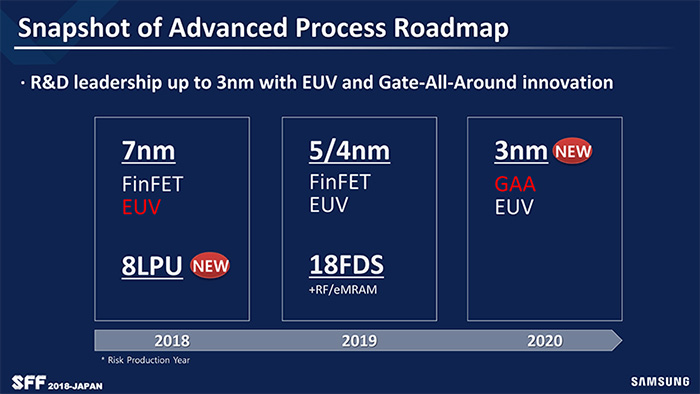

随着晶圆代工厂台积电及记忆体厂三星电子的7纳米逻辑制程均支援极紫外光(EUV)微影技术,并会在2019年进入量产阶段,半导体龙头英特尔也确定正在开发中的7纳米制程会支援新一代EUV技术。

英特尔10纳米制程推进不如预期,导致14纳米产能供不应求,并造成2018年第四季以来的处理器缺货问题,预期要等到2019年第二季才会获得纾解。英特尔日前已宣布将扩大资本支出提升产能,并且预期10纳米Ice Lake处理器将在今年第四季量产出货。

至于英特尔未来制程微缩计划,据外电报导,掌管英特尔制程及制造业务技术及系统架构事业的总裁兼首席工程师Murthy Renduchintala日前指出,10纳米制程与2014年订定的制程标准相同,不论性能、密度、功耗等都保持不变。另外,有了10纳米的制程研发经验,英特尔7纳米发展良好,并将加入新一代EUV微影技术,由于10纳米及7纳米是由不同团队开发,7纳米EUV制程不会受到10纳米制程延迟影响。不过,英特尔未提及7纳米何时可进入量产。

据猜测,英特尔原原计划10nm后第四年推出,所以就是2020年底,假如真能做到,那么10nm制程将会是最短命的一代制程。

按照估计,Intel可能还要配置多20~40台ASML的7nm EUV光刻机来达到月产10万片的能力。(7nm EUV光刻机单台售价1.2亿美元。)

业界指出,台积电及三星的7纳米EUV制程2019年逐步提升产能,但要开始真正大量进行投片量产,应该要等到2020年之后。英特尔的7纳米EUV制程要真正进入生产阶段,预期也要等到2020年或2021年之后。不过,以三大半导体厂的计划来看,EUV微影技术将成为7纳米及更先进制程的主流。

EUV光刻技术发展态势

光刻(lithography)为集成电路微细化的最关键技术。当前在16/14nm节点乃至10及7nm节点,芯片制造商普遍还在使用193nm ArF浸润式光刻机+多重成像技术,但采用多重成像技术后将增加曝光次数,导致成本显著上升及良率、产出下降等问题。根据相关企业的规划,在7/5nm节点,芯片生产将导入极紫外(EUV)光刻技术,EUV光刻使用13.5nm波长的极紫外光,能够形成更为精细的曝光图像。芯片厂商计划将EUV光刻应用到最困难的光刻工序,即金属1层以及过孔生成工序,而其他大部分工序则仍将延用193nm ArF浸润式光刻机+多重成像来制作。据EUV光刻机生产商阿斯麦(ASML)称,相比浸润式光刻+三重成像技术,EUV光刻技术能够将金属层的制作成本降低9%,过孔的制作成本降低28%。

EUV光刻的关键技术包括EUV光源和高数值孔径(NA)镜头,前者关乎光刻机的吞吐量(Throughput),后者关乎光刻机的分辨率(Resolution)和套刻误差(Overlay)能力等。目前,全球EUV光刻机生产基本上由荷兰阿斯麦公司所垄断,其最新 NXE:3400B EUV机型,采用245W光源,在实验条件下,未使用掩膜保护膜(pellicle),已实现每小时曝光140片晶圆的吞吐量;该机型在用户端的测试中,可达到每小时曝光125片晶圆的吞吐量,套刻误差2nm;按照阿斯麦公司EUV技术路线规划,公司将在2018年底前,通过技术升级使NXE:3400B EUV机型的套刻误差减小到1.7nm以下,满足5nm制程的工艺需求;在2019年中,采用250W EUV光源,达到每小时145片晶圆的量产吞吐量;在2020年,推出升级版的NXE:3400C EUV机型,采用250W EUV光源达到155片/时的量产吞吐量。总体上,目前的250W EUV光源已经可以满足7nm甚至5nm制程的要求,但针对下一代的EUV光源仍有待开发。据估算,在3nm技术节点,对EUV光源的功率要求将提升到500W,到了1nm技术节点,光源功率要求甚至将达到1KW。

高数值孔径(High-NA)光学系统方面,由于极紫外光会被所有材料(包括各种气体)吸收,因此极紫外光光刻必需在真空环境下,并且使用反射式透镜进行。目前,阿斯麦公司已开发出数值孔径为0.33的EUV光刻机镜头,阿斯麦正在为3nm及以下制程采开发更高数值孔径(NA)光学系统,公司与卡尔蔡司公司合作开发的数值孔径为0.5的光学系统,预计在2023-2024年后量产,该光学系统分辨率(Resolution)和生产时的套刻误差(Overlay)比现有系统高出70%,每小时可以处理 185 片晶圆。

除光刻机之外,EUV光刻要在芯片量产中应用仍有一些技术问题有待进一步解决,如:光刻胶、掩膜、掩膜保护薄膜(pellicle)。

光刻胶方面,要实现大规模量产要求光刻胶的照射反应剂量水平必须不高于20mJ/cm2。而目前要想得到完美的成像,EUV光刻胶的照射剂量普遍需要达到30-40mJ/cm2。在30mJ/cm2剂量水平,250w光源的EUV光刻机每小时吞吐量只能达到90片,显著低于理想的125片。由于EUV光刻产生的一些光子随机效应,要想降低光刻胶的照射剂量水平仍需克服一系列挑战。其中之一是所谓的光子发射噪声现象。光子是光的基本粒子,成像过程中照射光光子数量的变化会影响EUV光刻胶的性能,因此会产生一些不希望有的成像缺陷,比如:线边缘粗糙(line-edge roughness:LER)等。

光掩膜版,EUV光刻使用镜面反射光而不是用透镜折射光,因此EUV光刻采用的光掩膜版也需要改成反射型,改用覆盖在基体上的硅和钼层来制作。同时,EUV光刻对光掩膜版的准确度、精密度、复杂度要求比以往更高。当前制作掩膜版普遍使用的可变形状电子束设备(VSB),其写入时间成为最大的挑战,解决方案之一是采用多束电子束设备。包括IMS公司、NuFlare公司等已在开发相关多束电子束产品,多束电子束设备能够提高光掩膜版制作效率,降低成本,还有助于提高光掩膜版的良率。未来,大部分EUV光掩膜版仍可以使用可变形状电子束设备来制作,但是对少数复杂芯片而言,要想保持加工速度,必须使用多束电子束设备。

EUV薄膜,EUV薄膜作为光掩膜的保护层,提供阻隔外界污染的实体屏障,可以防止微尘或挥发气体污染光掩膜表面,减少光掩膜使用时的清洁和检验。阿斯麦公司已经开发出83%透射率的薄膜,在采用245W光源,测试可达到100 片晶圆/时吞吐量,阿斯麦的目标是开发出透射率90%的透明薄膜,可承受300W的EUV光源,实现125片晶圆/时的吞吐量。

初期,EUV光刻还是主要应用于高端逻辑芯片、存储芯片的生产,主要芯片企业已相继宣布了各自导入EUV光刻的计划。