近两年,中国芯片产业受到了严重打击,痛定思痛之余也让国人意识到芯片自主研发的重要性。从2008年以来,十年间,芯片都是我国第一大宗进口商品,进口额远超于排名第二的石油。2018年我国进口集成电路数量为4175.7亿个,集成电路进口额为3120.58亿美元,这组数据清晰的反映出我国中高端芯片技术能力的缺失及对外依赖的严重程度。

我国生产芯片的技术水平与国外先进企业相比存在较大的差距,且生产芯片的工具及工艺也被国外几个公司垄断。其中光刻机,被誉为人类20世纪的发明奇迹之一,是集成电路产业皇冠上的明珠,研发的技术门槛和资金门槛非常高。当今能够制造出光刻机的国家仅有荷兰、美国、日本等少数几个国家,荷兰的ASML是该领域绝对的龙头老大,它的光刻机占据全球市场的80%左右。

光刻机用途广泛,除了前端光刻机之外,还有用于LED制造领域投影光刻机和用于芯片封装的后道光刻机,在此只介绍前端光刻机。

1.背景技术及工作原理

光刻(lithography)设备是一种投影曝光系统,由紫外光源、光学镜片、对准系统等部件组装而成。在半导体制作过程中,光刻设备会投射光束,穿过印着图案的光掩膜版及光学镜片,将线路图曝光在带有光感涂层的硅晶圆上。通过蚀刻曝光或未受曝光的部份来形成沟槽,然后再进行沉积、蚀刻、掺杂,架构出不同材质的线路。

此工艺过程被一再重复,将数十亿计的MOSFET或其他晶体管建构在硅晶圆上,形成一般所称的集成电路。

光刻工艺在整个芯片制造过程中至关重要,其决定了半导体线路纳米级的加工度,对于光刻机的技术要求十分苛刻,对误差及稳定性的要求型极高,相关部件需要集成材料、光学、机电等领域最尖端的技术。因而光刻机的分辨率、精度也成为其性能的评价指数,直接影响到芯片的工艺精度以及芯片功耗、性能水平。

因此光刻机是集成电路制造中最庞大、最精密复杂、难度最大、价格最昂贵的设备。

光刻机的分辨率决定了IC的最小线宽。想要提高光刻机的成像分辨率,通常采用缩短曝光光源波长和增大投影物镜数值孔径两种方法。

根据所述光源的改进,光刻机经历了第一代是436nm g-line;第二代是365nm i-line;第三代是248nm KrF;第四代193nm ArF;最新的是13.5nm EUV。

其中,193nm ArF也被称为深紫外光源。使用193nmArF光源的干法光刻机,其光刻工艺节点可达45/40nm,由于当时光源波长难以进一步突破,因此业界采用了浸没技术等效缩小光源波长(193nm变化为134nm)的同时在液体中镜头的数值孔径得以提高(0.50-0.93变化为0.85-1.35)、且应用光学邻近效应矫正(OPC)等技术后,193nm ARF干法光刻极限工艺节点可达28nm。

到了28nm工艺节点之后,单次曝光图形间距已经无法进一步提升,业界开始采用Multiple patterning(多次曝光和刻蚀)的技术来提高图形密度但由此引入的掩膜使得生产工序增加,导致成本大幅上升,且良率问题也如影随行。

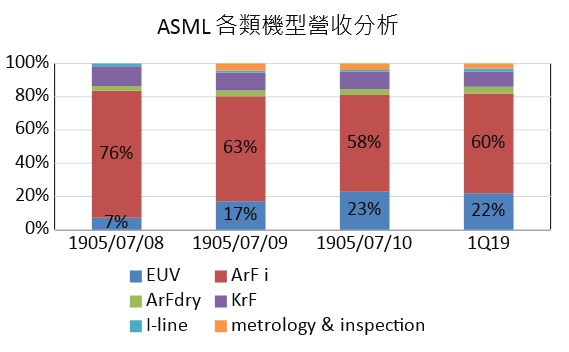

据悉,业内巨头台积电及英特尔的7nm工艺仍然在使用浸入式ArF的光刻设备,但沉浸式光刻终于7nm之后的下一代工艺节点,难以再次发展,EUV成为了解决这一问题的关键,目前EUV光刻机光源主要采用的办法是将准分子激光照射在锡等靶材上,激发出13.5nm的光子,作为光刻机光源。

各大Foundry厂在7nm以下的最高端工艺上都会采用EUV光刻机,其中三星在7nm节点上就已经采用了。而目前只有荷兰ASML一家能够提供可供量产用的EUV光刻机,国内的光刻机技术从20世纪70年代开始就先后有清华大学精密仪器系、中科学院光电技术研究所、中电科45所投入研制,目前国内厂商只有上海微电子(SMEE)及中国电科(CETC)旗下的电科装备,其中SMEE目前量产的性能最好的为90nm(193 ArF)光刻机与国际水平相差较大。

另一方面投影物镜是光刻机中最昂贵最复杂的部件之一,提高光刻机分辨率的关键是增大投影物镜的数值孔径。随着光刻分辨率和套刻精度的提高,投影物镜的像差和杂散光对成像质量的影响越来越突出。浸没式物镜的轴向像差,如球差和场曲较干式物镜增大了n倍,在引入偏振光照明后,投影物镜的偏振控制性能变得更加重要。在数值孔径不断增大的情况,如何保持视场大小及偏振控制性能,并严格控制像差和杂散光,是设计投影物镜面临的难题。

传统光刻机的投影物镜多采用全折射式设计方案,即物镜全部由旋转对准装校的透射光学元件组成。其优点是结构相对简单,易于加工与装校,局部杂散光较少。然而,大数值孔径全折射式物镜的设计非常困难。

为了校正场曲,必须使用大尺寸的正透镜和小尺寸的负透镜以满足佩茨瓦尔条件,即投影物镜各光学表面的佩茨瓦尔数为零。透镜尺寸的增加将消耗更多的透镜材料,大大提高物镜的成本;而小尺寸的负透镜使控制像差困难重重。

为了实现更大的数值孔径,近年来设计者普遍采用折反式设计方案。折反式投影物镜由透镜和反射镜组成。反射镜的佩茨瓦尔数为负,不再依靠增加正透镜的尺寸来满足佩茨瓦尔条件,使投影物镜在一定尺寸范围内获得更大的数值孔径成为可能。

数值孔径是光学镜头的一个重要指标产业化的光刻物镜工作波长经历了436nmG线,365nm线,248nmKRF,193nmArF和13.5nm极紫外,相应的物镜设计也在不断的提高数值孔径。

以现在世界主流的光刻机深紫外浸入式光刻机紫外光线来说要想达到22纳米的水平,那么物镜的数值口径要达到1.35以上,要达到这个口径很难,因为要加工亚纳米精度的大口径的镜片,用到的最大口径的镜片达到了400毫米。目前只有德国的光学公司可以达到,另外日本尼康通过购买德国的技术也可以达到。

虽然目前国内国防科大精密工程团队自主研制的磁流变和离子束两种超精抛光装备,实现了光学零件加工的纳米精度,但浸没式光刻物镜异常复杂,涵盖了光学、机械、计算机、电子学等多个学科领域最前沿,二十余枚镜片的初始结构设计难度极大——不仅要控制物镜波像差,更要全面控制物镜系统的偏振像差。因此,在现阶段国内物镜也无法完全替代进口产品。

2.专利分析

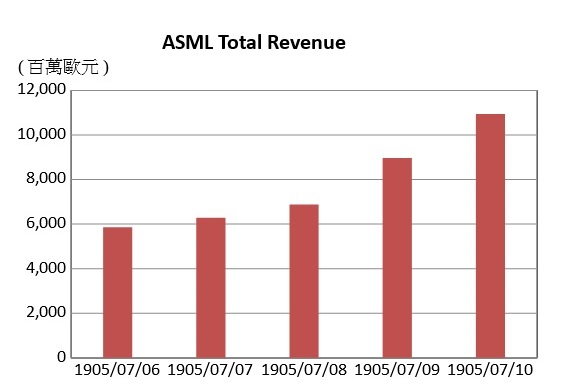

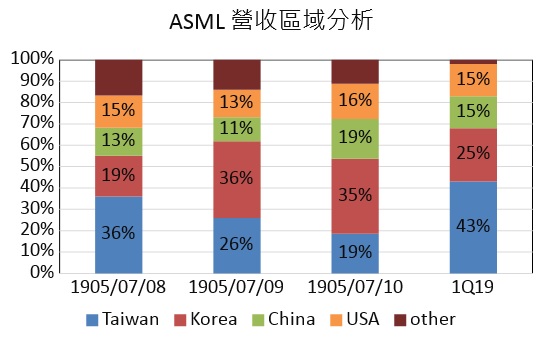

从国内外市场格局来看,ASML占据了全球主要的市场份额,而日本尼康其先进光刻机由于性能问题并未受到半导体制造商的青睐,目前主要经营为面板光刻机;佳能保留低端半导体i-line和Kr-F光刻机,退出了高端光刻机的角逐,从2019年ASML和尼康的财报可以进一步看出。

根据ASML的2019年第一季度财报,虽然其较2018年第四季度收益有所下降,但仍然有16.89亿欧元的营收,其中ArF Dry占据4%,KrF占据9%;i-line占据2%;Metrology&inspection占据3%;EUV占据22%;ArF Immersion占据60%。而尼康2019年财报,半导体光刻业务临时利润为15亿日元,约为9105万人民币,与ASML相距甚远。

国内光刻机虽与ASML相距甚远,但在曝光系统及双工作台系统也取得了一些成就:如2017年中科院院长春光精密机械与物理研究所牵头研发“极紫外光刻关键技术”通过验收;北京华卓荆轲科技股份有限公司成功打破了ASML在工作台上的技术垄断。

通过incopat工具对光刻机相关专利进行检索分析,得到该领域2000年至今的年申请趋势图,重点申请人申请数量排名,EUV光刻机重点申请人申请数量排名。

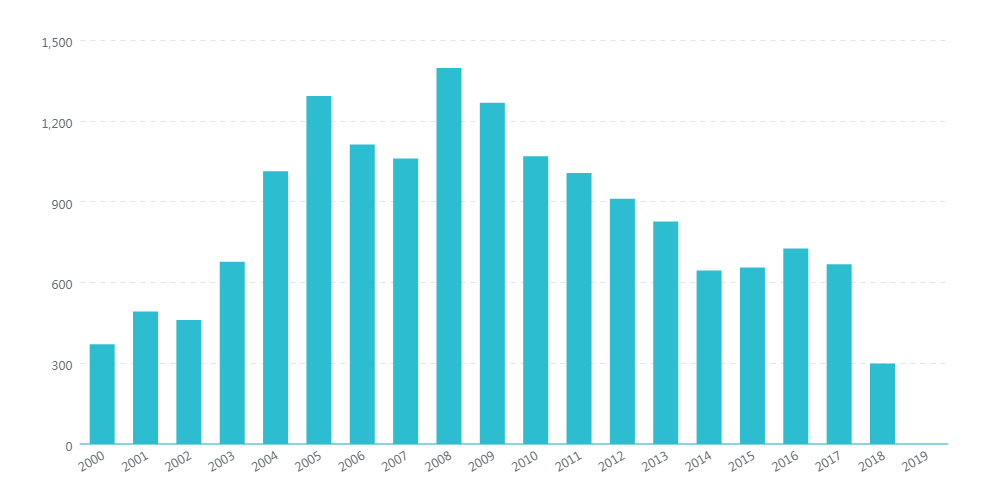

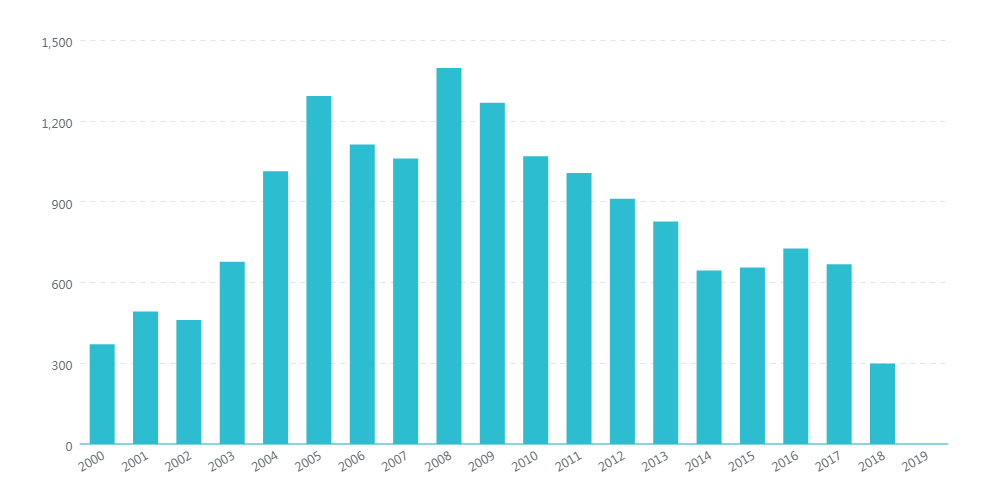

图1光刻机全球申请量趋势

数据来源:incopat,2000-2018年

从图1可以看出,2000-2004年迎来了光刻机专利申请的第一次快速增长,这一时期Intel、VIA及IBM等企业设计的半导体芯片性能快速提升,对半导体制程提出了越来越高的要求,光刻机技术不断提升,使得申请量也随之攀升。

而在光刻机研发到193nm时遇到瓶颈,ASML联手多家芯片巨头将193浸润式光科技树延伸至15nm,在此期间专利申请量下滑,但沉浸式光刻在7nm之后难以发展,EUV光刻机成为了解决这一问题的关键,因此近些年光刻机的相关技术专利申请呈现在此增长的趋势。

图2光刻机专利申请地域分布图

数据来源:incopat,2000-2018年

从地域分布来看,在光刻机领域,日本的专利申请量最多,日本企业除了在本国大量布局之外,比较重视在美国、韩国、中国台湾和中国大陆的专利布局,说明日本作为传统的光刻机领头羊,在中低端光刻机的研发投入了大量精力,布局了大量相关专利,其在中低端光刻技术上的实力雄厚。但在高端光刻机领域,日本技术仍有待提升。与之相比,中国相关专利申请量较少,说明光刻机技术门槛高,且国内没有过多的技术积累,发展较慢。

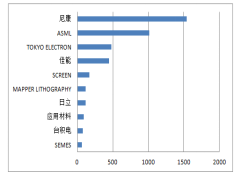

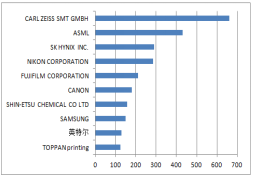

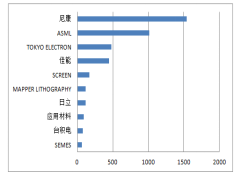

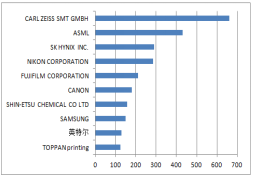

图3左图为光刻机重点申请人申请量排名;右图为EUV重点申请人申请量排名

数据来源:incopat,2008-2018年

图3为近几年关于EUV专利重点申请人排名与光刻机重点申请人申请排名比较,其中关于EUV光刻机重点申请人申请数量,ASML位列第二名,排名第一的光学仪器企业卡尔蔡司(Carl Zeiss)及排名较为靠前的海力士及三星均为ASML的合作伙伴,日本尼康及佳能分别位列第四及第六位。

对比光刻机重点申请人专利申请数量及EUV光刻机重点申请人专利申请数量,不难看出日本佳能及尼康在EUV光刻机研究上已经与ASML拉开较大差距,逐渐退出高端光刻机额角逐,究其原因为:

(1)ASML无上下游企业,专注研发,且核心技术绝对保密;

(2)ASML的特殊规定:想获得ASML光刻机的优先使用权的企业,需入股ASML,台积电,三星,英特尔,海力士纷纷入股,以寻求互惠互利。如在光刻机进入193nm节点时,ASML与台积电联合开发的浸润式光刻机是奠定ASML绝对霸主的关键一步。

(3)ASML每年将营业额的15%用于研发,高额的研发费用,让尼康和佳能望而却步,逐步退出高端光刻机的角逐。

3.结论

光刻机在芯片制造过程中起着至关重要的作用,随着器件特征尺寸的不断缩小,对光刻机的精度要求越来越高,作为芯片制造业巨头:三星、台积电、因特尔已纷纷入股ASML,以谋求其高端光刻设备共同开发与优先采购权,国内光刻机领域虽然取得一些进展,但仍然与国际水平差距巨大,仅仅依靠进口,国内的芯片制造行业势必受制于人,加快光刻机的研制步伐,刻不容缓。

参考文献:

[1]http://www.sohu.com/a/213887254_468750

[2]徐明飞.2017.高数值孔径投影光刻物镜的光学设计[D]

[3]http://blog.sina.com.cn/s/blog_bde252a80102woqm.html

[4]程建瑞.2015.EUV光刻技术的挑战[J].电子工业专用设备.

[5]张金颖.2019.荷兰光刻巨头崛起对我国发展核心技术的启示[J].中国工业和信息化.

[6]王龙兴.2018.全球半导体设备的市场分析[J].上海市集成电路行业协会.

● 作者:超凡知识产权数据与咨询事业部检索分析师 王辉